**REVIEW OF RESEARCH**

IMPACT FACTOR : 5.7631(UIF) UGC APPROVED JOURNAL NO. 48514

ISSN: 2249-894X

VOLUME - 8 | ISSUE - 4 | JANUARY - 2019

# **CMOS FABRICATION: AN OVERVIEW**

Jyotindra Kumar Research Scholar, L.N.M.U. Darbhanga.

### **ABSTRACT :**

The rationale is that the electronic properties of a semiconductor like semiconducting material square measure very sensitive to impurity concentrations. Impurity levels measured at components per million or less will have dramatic effects on carrier mobilities, lifetimes, etc. it's so necessary to any purify the MGS in what's referred to as electronic grade semiconducting material (EGS). EGS is created from the chlorination of grounded MGS as result of the reaction product square measure liquids at temperature, ultrapure EGS may be obtained from fractionation and chemical reduction processes.

**KEYWORDS** : electronic properties , electronic grade semiconducting material (EGS).

#### **INTRODUCTION**

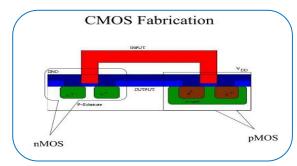

The resultant EGS is within the type of crystalline chunks. This paper presents a short summary of CMOS method integration. method integration refers to the well-defined assortment of semiconductor processes needed to fabricate CMOS integrated circuits ranging from virgin semiconducting material wafers. [1-5] furthermore, there square measure sturdy interactions between circuit style and method integration. For example, the everyday style rule set is set in massive half by the constraints within the fabrication processes. Hence, circuit designers, method engineers, and integration engineers square measure needed to speak effectively. [1] to the present finish, we tend to initial examine the basic processes, known as unit processes, needed for CMOS fabrication. The first focus is that the qualitative understanding of the processes with restricted introduction of quantitative expressions. The unit processes square measure combined during a deliberate sequence to fabricate CMOS.

### **CMOS UNIT PROCESSES**

In this section we tend to introduce every of the foremost processes needed within the fabrication of CMOS integrated circuits. we tend to initial discuss wafer production. Though wafer production isn't a unit method, it's yet vital to gift the assembly methodology that is employed by wafer makers. All ulterior discussions square measure targeted on the unit processes incorporated by fabrication facilities to provide integrated circuits. The unit processes square measure sorted by practicality.[1] Thermal reaction, doping

processes, lithography, thin-film removal, and thin-film deposition techniques square measure conferred.

Wafer Manufacture Silicon is that the second most abundant part within the Earth's crust; but, it happens completely in compounds. In fact, elemental semiconducting material could be a synthetic material that's refined from these varied compounds. The foremost common is silicon dioxide (impure  $SiO_2$ ). fashionable integrated circuits should be invented on ultrapure, defect-free slices of single crystalline semiconducting material known as wafers.

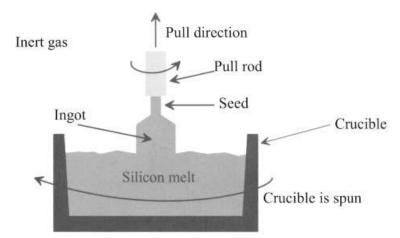

Semiconducting material refinement, crystal growth, and wafer formation. Semiconducting material refinement begins with the reduction of silicon dioxide in Associate in Nursing arc chamber at roughly 2000°C with a carbon supply. The carbon effectively "pulls" the chemical element from the SiO2 molecules, so with chemicals reducing the SiO<sub>2</sub> into roughly ninety eight pure semiconducting material stated as science grade semiconducting material (MGS).

Figure 1 Simplified diagram showing Czochralski (CZ) crystal growth.

## REFERENCES

[1] B.J. Blalock, P.E. Allen, G.A. Rincon-Mora, Designing 1-V op amps using standard digital CMOS technology, IEEE Trans. Circuits Syst.Analog Digital Signal Process. 45 (1998) 769–780.

[2] J. Rosenfeld, M. Kozak, E.G. Friedman, A bulk-driven CMOS OTA with 68 dB DC gain, IEEE International Conference on Electronics, Circuits and Systems. (ICECS 2004) 5–8.

[3] J. Rosenfeld, M. Kozak, E.G. Friedman, A 0.8 V high performance OTA using bulk-driven MOSFETs for low power mixed-signal SOCs, IEEE International Conference on SOC. (2003) 245–246.

[4] R. He, L. Zhang, Evaluation of modern MOSFET models for bulk-driven applications, 51st Midwest Symposium on Circuits and Systems. (MWSCAS (2008) 105–108.

[5] Christian Je´ sus B. Fayomi, M. Sawan, G. Roberts, Reliable circuit techniques for low-voltage analog design in deep submicron standard CMOS: a tutorial, Analog Integr. Circuits Signal Process. 39 (2004) 21–38.