# REVIEW OF RESEARCH

UGC APPROVED JOURNAL NO. 48514

ISSN: 2249-894X

VOLUME - 8 | ISSUE - 3 | DECEMBER - 2018

# **CMOS CIRCUIT FABRICATION: AN OVERVIEW**

Jyotindra Kumar Research Scholar , L.N.M.U. Darbhanga.

#### **ABSTRACT**

The CMOS circuit style method consists of process circuit inputs and outputs, hand calculations, circuit simulations, circuit layout, simulations as well as parasitics, valuation of circuit inputs and outputs, fabrication, and testing.

**KEYWORDS:** circuit style method, parasitics, valuation of circuit inputs.

#### **INTRODUCTION**

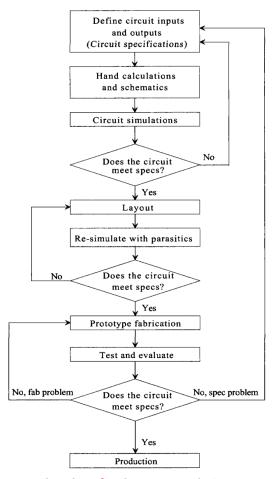

A flow sheet of this method is shown in Fig. 1. The circuit specifications square measure seldom set in concrete; that's, they will modification because the project matures. [1-5] This could be the results of trade-offs created between price and performance, changes within the marketability of the chip, or just changes within the customer's wants. In most cases, major changes when the chip has gone into production aren't doable. This text concentrates on custom IC style. Different (noncustom) ways of coming up with chips, as well as field-programmable-gate-arrays (FPGAs) and voltaic cell libraries, square measure used once low volume and fast style turnaround square measure necessary. Most chips that square measure mass made, as well as microprocessors and memory, square measure samples of chips that square measure bespoke.

## **FABRICATION**

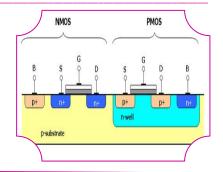

The task of birthing out the IC is commonly given to a layout designer. However, it's very necessary that the engineer will lay out a chip (and will offer direction to the layout designer on the way to layout a chip) and perceive the parasitics concerned within the layout. Parasitics square measure the stray capacitances, inductances, pn junctions, and bipolar transistors, with the associated issues (breakdown, keep charge, latch-up, etc.). A elementary understanding of those issues is vital in precision/high-speed style.

Journal for all Subjects: www.lbp.world

Figure 1 Flowchart for the CMOS IC design process.

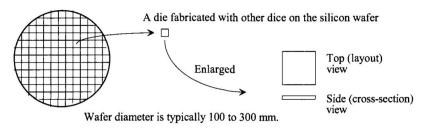

CMOS integrated circuits area unit fictional on skinny circular slices of atomic number 14 known as wafers. Every wafer contains many (perhaps a whole bunch or maybe thousands) of individual chips or "die" (Fig. 2). For production functions, every die on a wafer is sometimes identical, as seen within the photograph in Fig. 2. Additional to the wafer area unit take a look at structures and method monitor plugs (sections of the wafer accustomed monitor method parameters). the foremost common wafer size (diameter) in production at the time of this writing is three hundred millimetre (12 inch).

Figure 2 CMOS integrated circuits are fabricated on and in a silicon wafer.

The ICs we have a tendency to style and lay out employing a layout program is fictitious through MOSIS (http://mosis.com) on what's referred to as a multiproject wafer; that's, a wafer that's comprised of chip styles of varied sizes from totally different sources (educational, private, government, etc.). MOSIS combines multiple chips on a wafer to separate the pleasing value among many styles to stay the price low. MOSIS subcontracts the fabrication of the chip styles (multiproject wafer) intent on one in all several business makers (vendors). MOSIS takes the wafers it receives from the vendors, when fabrication, and cuts them up to isolate the individual chip styles. The chips square measure then packaged and sent to the conceiver.

### **REFERENCES**

- [1] F. Khateb, N. Khatib, D. Kuba´ nek, Novel low-voltage low-power high- precision CCII 7 based on bulk-driven folded cascode OTA, Microelectron. J. 42 (2011) 622–631.

- [2] B.J. Blalock, P.E. Allen, A low-voltage, bulk-driven MOSFET current mirror for CMOS technology', IEEE Int. Symp. Circuits Syst. 3 (1995) 1972–1975.

- [3] L. Yani, Y. Yintang, Z. Zhangming, A novel low-voltage low-power bulk-driven cascade current mirror, 3rd International Conference on Advanced Computer Theory and Engineering. 3 (ICACTE 2010) V3-78–V3-83.

- [4] Z. Zhu, J. Mo, Y. Yang, A low voltage bulk-driving PMOS cascode current mirror, 9th International Conference on Solid-State and Integrated-Circuit Technology. (ICSICT 2008) 2008–2011.

- [5] J. Saraoa, Z.J. Wanga, Y.L. Wub, H.L. Kwok, An improved regulated cascode current mirror, Solid-State Electron. 46 (2002) 307–312.